Serial Multiplier Vhdl Code

Each of these technologies customize the implementation adding different features depending on the type of FPGA you are using. Peer Data Program For Mac

multiplier vhdl code

Each of these technologies customize the implementation adding different features depending on the type of FPGA you are using. 518b7cbc7d Peer Data Program For Mac

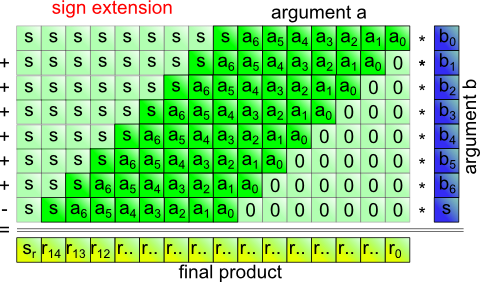

booth multiplier vhdl code

multiplier vhdl code, 4 bit multiplier vhdl code, booth multiplier vhdl code, 2 bit multiplier vhdl code, 8 bit multiplier vhdl code, 16 bit multiplier vhdl code, n bit multiplier vhdl code, 4 bit multiplier vhdl code structural, floating point multiplier vhdl code, 8 bit multiplier vhdl code structural, array multiplier vhdl code, booth multiplier vhdl code with testbench, dadda multiplier vhdl code, vedic multiplier vhdl code, multiplier accumulator vhdl code, 2x2 multiplier vhdl code, complex multiplier vhdl code, parallel multiplier vhdl code Update Nvidia Drivers For Mac

Implementation of these arithmetic functions results in efficient resource usage and improved performance for DSP applications.. Such dedicated hardware resource generally implements 18×18 multiply and accumulate function that can be used for efficient implementation of complex DSP algorithms such as finite impulse response (FIR) filters, infinite impulse response (IIR) filters, and fast fourier transform (FFT) for filtering and image processing applications etc.. In addition to the basic MACC function, DSP algorithms typically need small amounts of RAM for coefficients and larger RAMs for data storage.. Therefore, four input ports and four output ports of data type ’bit’ are required. Haynes Manual Nissan Almera